# SiFive U74-MC Core Complex Manual 21G2.01.00

Copyright © 2021 by SiFive, Inc. All rights reserved.

# **SiFive U74-MC Core Complex Manual**

### **Proprietary Notice**

Copyright © 2021 by SiFive, Inc. All rights reserved.

SiFive U74-MC Core Complex Manual by SiFive, Inc. is licensed under Attribution-NonCommercialNoDerivatives 4.0 International. To view a copy of this license, visit: http://creativecommons.org/licenses/by-nc-nd/4.0

Information in this document is provided "as is," with all faults.

SiFive expressly disclaims all warranties, representations, and conditions of any kind, whether express or implied, including, but not limited to, the implied warranties or conditions of merchantability, fitness for a particular purpose and non-infringement.

SiFive does not assume any liability rising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation indirect, incidental, special, exemplary, or consequential damages.

SiFive reserves the right to make changes without further notice to any products herein.

# **Contents**

| Lis | st o         | f Tabl | es                                           | 12 |  |

|-----|--------------|--------|----------------------------------------------|----|--|

| Lis | st o         | f Figu | ıres                                         | 18 |  |

| 1   | Introduction |        |                                              |    |  |

|     | 1.1          | Abou   | t this Document                              | 22 |  |

|     | 1.2          | Abou   | t this Release                               | 23 |  |

|     | 1.3          | U74-I  | MC Core Complex Overview                     | 23 |  |

|     | 1.4          | S7 RI  | ISC-V Monitor Core                           | 24 |  |

|     | 1.5          | U7 R   | ISC-V Application Cores                      | 25 |  |

|     | 1.6          | Interr | upts                                         | 25 |  |

|     | 1.7          | Debu   | g Support                                    | 26 |  |

|     | 1.8          | Comp   | oliance                                      | 26 |  |

| 2   |              |        | Abbreviations and Terms                      |    |  |

| 3   |              |        | C-V Core                                     |    |  |

|     | 3.1          |        | orted Modes                                  |    |  |

|     | 3.2          |        | iction Memory System                         |    |  |

|     |              | 3.2.1  | Execution Memory Space                       |    |  |

|     |              | 3.2.2  | L1 Instruction Cache                         |    |  |

|     |              | 3.2.3  | Cache Maintenance                            |    |  |

|     |              | 3.2.4  | Coherence with Higher Level Caches           |    |  |

|     |              | 3.2.5  | Instruction Tightly-Integrated Memory (ITIM) |    |  |

|     |              | 3.2.6  | Instruction Fetch Unit                       |    |  |

|     | 2.2          | 3.2.7  | Branch Prediction                            |    |  |

|     | 3.3          |        | ution Pipeline                               |    |  |

|     | 3.4          |        | Memory System                                |    |  |

|     |              | J.4.1  | Dala Huhuv-Ilileuraleu Mehory (DTIM)         | ວວ |  |

|   | 3.5 | Fast I | /0                                                 | 35 |

|---|-----|--------|----------------------------------------------------|----|

|   | 3.6 | Atomi  | ic Memory Operations                               | 35 |

|   | 3.7 | Physi  | cal Memory Protection (PMP)                        | 36 |

|   |     | 3.7.1  | PMP Functional Description                         | 36 |

|   |     | 3.7.2  | PMP Region Locking                                 | 36 |

|   |     | 3.7.3  | PMP Registers                                      | 37 |

|   |     | 3.7.4  | PMP and PMA                                        | 39 |

|   |     | 3.7.5  | PMP Programming Overview                           | 39 |

|   |     | 3.7.6  | PMP and Paging                                     | 41 |

|   |     | 3.7.7  | PMP Limitations                                    | 41 |

|   |     | 3.7.8  | Behavior for Regions without PMP Protection        | 41 |

|   |     | 3.7.9  | Cache Flush Behavior on PMP Protected Region       | 42 |

|   | 3.8 | Hardv  | vare Performance Monitor                           | 42 |

|   |     | 3.8.1  | Performance Monitoring Counters Reset Behavior     | 42 |

|   |     | 3.8.2  | Fixed-Function Performance Monitoring Counters     | 42 |

|   |     | 3.8.3  | Event-Programmable Performance Monitoring Counters | 43 |

|   |     | 3.8.4  | Event Selector Registers                           | 43 |

|   |     | 3.8.5  | Event Selector Encodings                           | 43 |

|   |     | 3.8.6  | Counter-Enable Registers                           | 45 |

|   | 3.9 | Ports  |                                                    | 45 |

|   |     | 3.9.1  | Front Port                                         | 45 |

|   |     | 3.9.2  | Memory Port                                        | 46 |

|   |     | 3.9.3  | Peripheral Port                                    | 46 |

|   |     | 3.9.4  | System Port                                        | 46 |

| _ |     |        |                                                    |    |

| 4 | U7  |        | C-V Core                                           |    |

|   | 4.1 |        | orted Modes                                        |    |

|   | 4.2 | Instru | ction Memory System                                |    |

|   |     | 4.2.1  | Execution Memory Space                             |    |

|   |     | 4.2.2  | L1 Instruction Cache                               |    |

|   |     | 4.2.3  | Cache Maintenance                                  |    |

|   |     | 4.2.4  | Coherence with Higher Level Caches                 |    |

|   |     | 4.2.5  | Instruction Fetch Unit                             | 49 |

|     | 4.2.6  | Branch Prediction                                             | 49 |

|-----|--------|---------------------------------------------------------------|----|

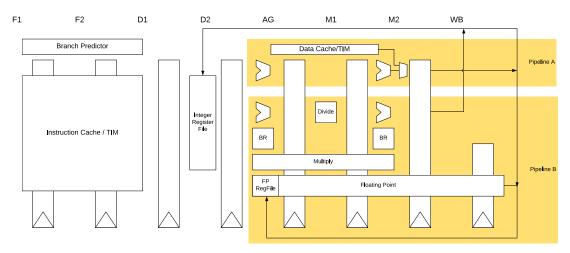

| 4.3 | Execu  | ution Pipeline                                                | 51 |

| 4.4 | Data   | Memory System                                                 | 52 |

|     | 4.4.1  | L1 Data Cache                                                 | 53 |

|     | 4.4.2  | Cache Maintenance Operations                                  | 53 |

|     | 4.4.3  | L1 Data Cache Coherency                                       | 53 |

|     | 4.4.4  | Coherence with Higher Level Caches                            | 53 |

| 4.5 | Atomi  | c Memory Operations                                           | 54 |

| 4.6 | Floati | ng-Point Unit (FPU)                                           | 54 |

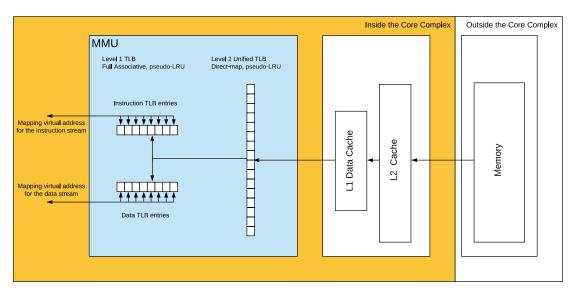

| 4.7 | Virtua | l Memory Support                                              | 54 |

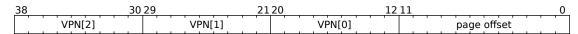

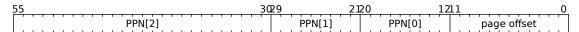

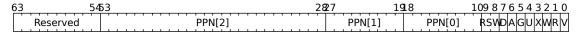

|     | 4.7.1  | Address and Page Table Formats                                | 56 |

|     | 4.7.2  | Supervisor Address Translation and Protection Register (SATP) | 58 |

|     | 4.7.3  | Supervisor Memory-Management Fence Instruction (SFENCE.VMA)   | 60 |

|     | 4.7.4  | Scenarios that Require SFENCE.VMA Instruction                 | 61 |

|     | 4.7.5  | Trap Virtual Memory                                           | 62 |

|     | 4.7.6  | Virtual Address Translation Process                           | 62 |

|     | 4.7.7  | Virtual-to-Physical Mapping Example                           | 63 |

|     | 4.7.8  | MMU at Reset                                                  | 66 |

| 4.8 | Physi  | cal Memory Protection (PMP)                                   | 66 |

|     | 4.8.1  | PMP Functional Description                                    | 66 |

|     | 4.8.2  | PMP Region Locking                                            | 67 |

|     | 4.8.3  | PMP Registers                                                 | 67 |

|     | 4.8.4  | PMP and PMA                                                   | 69 |

|     | 4.8.5  | PMP Programming Overview                                      | 69 |

|     | 4.8.6  | PMP and Paging                                                | 71 |

|     | 4.8.7  | PMP Limitations                                               | 71 |

|     | 4.8.8  | Behavior for Regions without PMP Protection                   | 71 |

|     | 4.8.9  | Cache Flush Behavior on PMP Protected Region                  | 72 |

| 4.9 | Hardv  | vare Performance Monitor                                      | 72 |

|     | 4.9.1  | Performance Monitoring Counters Reset Behavior                | 72 |

|     | 4.9.2  | Fixed-Function Performance Monitoring Counters                | 72 |

|     | 4.9.3  | Event-Programmable Performance Monitoring Counters            | 73 |

|     | 4.9.4  | Event Selector Registers                                      | 73 |

|   |      | 4.9.5  | Event Selector Encodings                               | 73 |

|---|------|--------|--------------------------------------------------------|----|

|   |      | 4.9.6  | Counter-Enable Registers                               | 75 |

|   | 4.10 | ) Port | ts                                                     | 75 |

|   |      | 4.10.1 | Front Port                                             | 76 |

|   |      | 4.10.2 | Memory Port                                            | 76 |

|   |      | 4.10.3 | Peripheral Port                                        | 76 |

|   |      | 4.10.4 | System Port                                            | 76 |

| 5 | Ph   | nysica | al Memory Attributes and Memory Map                    | 78 |

|   | 5.1  | Phys   | ical Memory Attributes Overview                        | 78 |

|   | 5.2  | Mem    | ory Мар                                                | 80 |

| 6 | Pr   | ograr  | nmer's Model                                           | 81 |

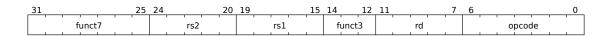

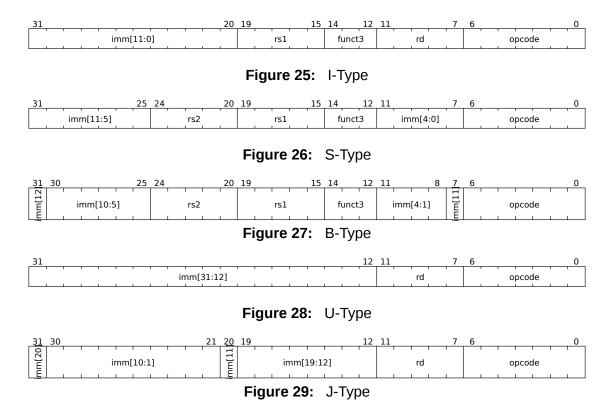

|   | 6.1  | Base   | Instruction Formats                                    | 81 |

|   | 6.2  | I Exte | ension: Standard Integer Instructions                  | 82 |

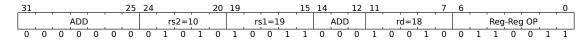

|   |      | 6.2.1  | R-Type (Register-Based) Integer Instructions           | 83 |

|   |      | 6.2.2  | I-Type Integer Instructions                            | 84 |

|   |      | 6.2.3  | I-Type Load Instructions                               | 85 |

|   |      | 6.2.4  | S-Type Store Instructions                              | 86 |

|   |      | 6.2.5  | Unconditional Jumps                                    | 87 |

|   |      | 6.2.6  | Conditional Branches                                   | 88 |

|   |      | 6.2.7  | Upper-Immediate Instructions                           | 89 |

|   |      | 6.2.8  | Memory Ordering Operations                             | 89 |

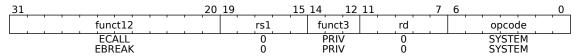

|   |      | 6.2.9  | Environment Call and Breakpoints                       | 90 |

|   |      | 6.2.10 | NOP Instruction                                        | 90 |

|   | 6.3  | M Ex   | tension: Multiplication Operations                     | 90 |

|   |      | 6.3.1  | Division Operations                                    | 91 |

|   | 6.4  | A Ext  | tension: Atomic Operations                             | 91 |

|   |      | 6.4.1  | Atomic Load-Reserve and Store-Conditional Instructions | 91 |

|   |      | 6.4.2  | Atomic Memory Operations (AMOs)                        | 92 |

|   | 6.5  | F Ext  | tension: Single-Precision Floating-Point Instructions  | 93 |

|   |      | 6.5.1  | Floating-Point Control and Status Registers            | 93 |

|   |      | 6.5.2  | Rounding Modes                                         | 94 |

|      | 6.5.3   | Single-Precision Floating-Point Load and Store Instructions      | 92  |

|------|---------|------------------------------------------------------------------|-----|

|      | 6.5.4   | Single-Precision Floating-Point Computational Instructions       | 95  |

|      | 6.5.5   | Single-Precision Floating-Point Conversion and Move Instructions | 95  |

|      | 6.5.6   | Single-Precision Floating-Point Compare Instructions             | 98  |

| 6.6  | D Ext   | ension: Double-Precision Floating-Point Instructions             | 99  |

|      | 6.6.1   | Double-Precision Floating-Point Load and Store Instructions      | 99  |

|      | 6.6.2   | Double-Precision Floating-Point Computational Instructions       | 100 |

|      | 6.6.3   | Double-Precision Floating-Point Conversion and Move Instructions | 101 |

|      | 6.6.4   | Double-Precision Floating-Point Compare Instructions             | 104 |

|      | 6.6.5   | Double-Precision Floating-Point Classify Instruction             | 105 |

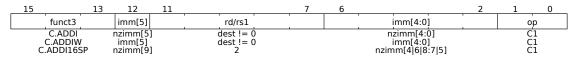

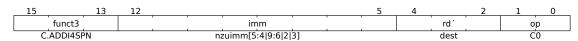

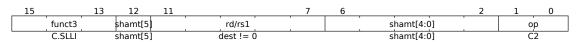

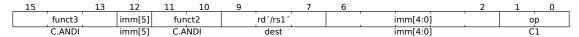

| 6.7  | C Ext   | ension: Compressed Instructions                                  | 105 |

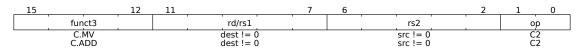

|      | 6.7.1   | Compressed 16-bit Instruction Formats                            | 105 |

|      | 6.7.2   | Stack-Pointed-Based Loads and Stores                             | 106 |

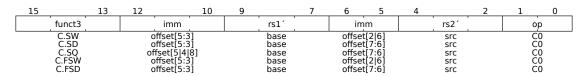

|      | 6.7.3   | Register-Based Loads and Stores                                  | 107 |

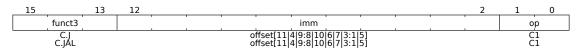

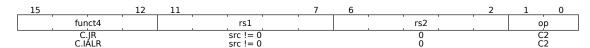

|      | 6.7.4   | Control Transfer Instructions                                    | 108 |

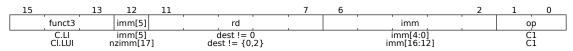

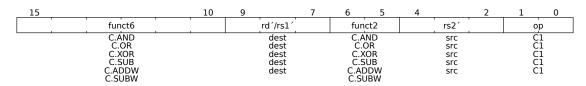

|      | 6.7.5   | Integer Computational Instructions                               | 109 |

| 6.8  | B Exte  | ension: Bit Manipulation Instructions                            | 112 |

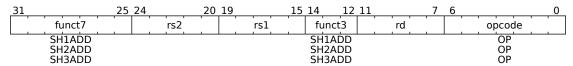

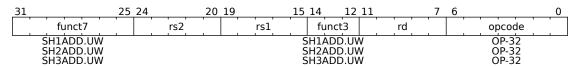

|      | 6.8.1   | Zba Extension                                                    | 112 |

|      | 6.8.2   | Zbb Extension                                                    | 113 |

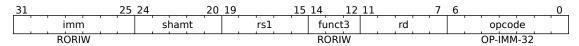

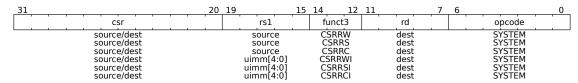

| 6.9  | Zicsr   | Extension: Control and Status Register Instructions              | 117 |

|      | 6.9.1   | Control and Status Registers                                     | 119 |

|      | 6.9.2   | Defined CSRs                                                     | 119 |

|      | 6.9.3   | CSR Access Ordering                                              | 123 |

|      | 6.9.4   | SiFive RISC-V Implementation Version Registers                   | 123 |

|      | 6.9.5   | Custom CSRs                                                      | 125 |

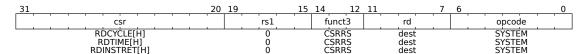

| 6.10 | ) Base  | e Counters and Timers                                            | 126 |

|      | 6.10.1  | Timer Register                                                   | 127 |

|      | 6.10.2  | Timer API                                                        | 127 |

| 6.11 | L Privi | leged Instructions                                               | 128 |

|      | 6.11.1  | Machine-Mode Privileged Instructions                             | 128 |

|      | 6.11.2  | Supervisor-Mode Privileged Instructions                          | 129 |

| 6.12 | 2 ABI   | - Register File Usage and Calling Conventions                    | 129 |

|      | 6.12.1  | RISC-V Assembly                                                  | 131 |

|   | (    | 5.12.2  | Assembler to Machine Code               | . 131 |

|---|------|---------|-----------------------------------------|-------|

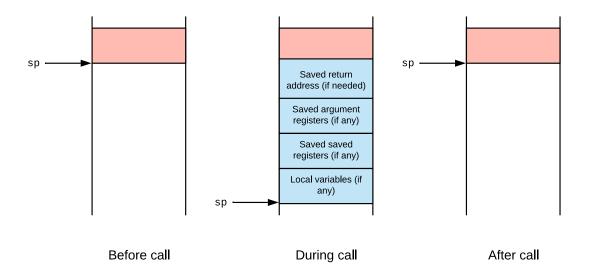

|   | (    | 5.12.3  | Calling a Function (Calling Convention) | 133   |

|   | 6.13 | Mem     | ory Ordering - FENCE Instructions       | . 135 |

|   | 6.14 | Boot    | Flow                                    | . 136 |

|   | 6.15 | Linke   | r File                                  | . 137 |

|   | (    | 5.15.1  | Linker File Symbols                     | . 138 |

|   | 6.16 | RISC    | :-V Compiler Flags                      | . 139 |

|   | (    | 5.16.1  | arch, abi, and mtune                    | . 139 |

|   | 6.17 | Com     | oilation Process                        | .143  |

|   | 6.18 | Large   | e Code Model Workarounds                | .143  |

|   | (    | 5.18.1  | RISC-V Code Model Summary               | 144   |

|   | (    | 5.18.2  | Enabling the Compact Code Model         | 144   |

|   | 6.19 | Pipeli  | ine Hazards                             | . 145 |

|   | (    | 5.19.1  | Read-After-Write Hazards                | . 145 |

|   | (    | 5.19.2  | Write-After-Write Hazards               | .146  |

|   | 6.20 | Read    | ling CSRs                               | . 146 |

|   |      |         |                                         |       |

| 7 | Cus  | stom    | Instructions and CSRs                   | 148   |

|   | 7.1  | CFLUSI  | H.D.L1                                  | . 148 |

|   | 7.2  | CDISC   | ARD.D.L1                                | . 148 |

|   | 7.3  | CEASE   |                                         | . 149 |

|   | 7.4  | PAUSE   |                                         | . 149 |

|   | 7.5  | Branch  | n Prediction Mode CSR                   | . 149 |

|   | 7.6  | SiFive  | Feature Disable CSR                     | . 150 |

|   | 7.7  | Other   | Custom Instructions                     | . 151 |

|   |      |         |                                         |       |

| 8 | Inte | errupt  | ts and Exceptions                       | .152  |

|   | 8.1  | Interru | pt Concepts                             | . 152 |

|   | 8.2  | Except  | tion Concepts                           | . 152 |

|   | 8.3  | Trap C  | Concepts                                | . 154 |

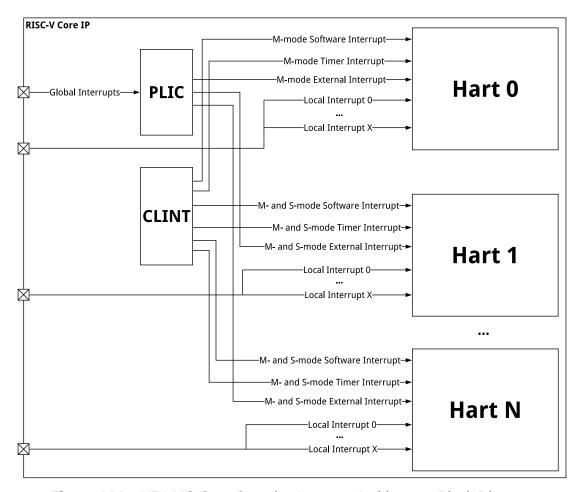

|   | 8.4  | Interru | pt Block Diagram                        | . 155 |

|   | 8.5  | Local I | Interrupts                              | . 156 |

|   | 8.6  | Interru | pt Operation                            | . 157 |

|   |      | 8.6.1   | Interrupt Entry and Exit                   | 157 |

|---|------|---------|--------------------------------------------|-----|

|   | 8.7  | Interru | upt Control and Status Registers           | 157 |

|   |      | 8.7.1   | Machine Status Register (mstatus)          | 158 |

|   |      | 8.7.2   | Machine Trap Vector (mtvec)                | 158 |

|   |      | 8.7.3   | Machine Interrupt Enable (mie)             | 160 |

|   |      | 8.7.4   | Machine Interrupt Pending (mip)            | 160 |

|   |      | 8.7.5   | Machine Cause (mcause)                     | 161 |

|   |      | 8.7.6   | Minimum Interrupt Configuration            | 162 |

|   | 8.8  | Super   | rvisor Mode Interrupts                     | 163 |

|   |      | 8.8.1   | Delegation Registers (mideleg and medeleg) | 163 |

|   |      | 8.8.2   | Supervisor Status Register (sstatus)       | 164 |

|   |      | 8.8.3   | Supervisor Interrupt Enable Register (sie) | 165 |

|   |      | 8.8.4   | Supervisor Interrupt Pending (sip)         | 165 |

|   |      | 8.8.5   | Supervisor Cause Register (scause)         | 166 |

|   |      | 8.8.6   | Supervisor Trap Vector (stvec)             | 167 |

|   |      | 8.8.7   | Delegated Interrupt Handling               | 168 |

|   | 8.9  | Interru | upt Priorities                             | 169 |

|   | 8.10 | ) Inter | rupt Latency                               | 169 |

|   | 8.11 | L Non-  | -Maskable Interrupt                        | 170 |

|   |      | 8.11.1  | Handler Addresses                          | 170 |

|   |      | 8.11.2  | RNMI CSRs                                  | 170 |

|   |      | 8.11.3  | MNRET Instruction                          | 171 |

|   |      | 8.11.4  | RNMI Operation                             | 171 |

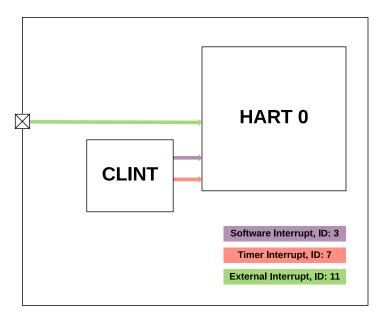

| 9 | Co   | ore-Lo  | ocal Interruptor (CLINT)                   | 172 |

|   | 9.1  | CLIN    | T Priorities and Preemption                | 172 |

|   | 9.2  | CLIN    | T Vector Table                             | 173 |

|   | 9.3  | CLIN    | T Interrupt Sources                        | 175 |

|   | 9.4  | CLIN    | T Interrupt Attribute                      | 175 |

|   | 9.5  | CLIN    | T Memory Map                               | 176 |

|   | 9.6  | Regis   | ster Descriptions                          | 176 |

|   |      | 9.6.1   | MSIP Register                              | 176 |

|   |      | 9.6.2   | Timer Registers                            | 177 |

|    | 9.7   | Super  | visor Mode Delegation               | 177 |

|----|-------|--------|-------------------------------------|-----|

| 10 | Pla   | atfori | m-Level Interrupt Controller (PLIC) | 178 |

|    | 10.1  | Mem    | ory Map                             | 179 |

|    | 10.2  | Interi | rupt Sources                        | 183 |

|    | 10.3  | Interi | rupt Priorities                     | 184 |

|    | 10.4  | Interi | rupt Pending Bits                   | 184 |

|    | 10.5  | Interi | rupt Enables                        | 185 |

|    | 10.6  | PLIC   | Clock Gate Disable                  | 186 |

|    | 10.7  | Prior  | ity Thresholds                      | 187 |

|    | 10.8  | Interi | rupt Claim Process                  | 187 |

|    | 10.9  | Interi | rupt Completion                     | 187 |

|    | 10.10 | Exa    | ımple PLIC Interrupt Handler        | 188 |

| 11 | Til   | eLin   | k Error Device                      | 189 |

| 12 | Вι    | ıs-Er  | ror Unit                            | 190 |

|    | 12.1  | Bus-   | Error Unit Overview                 | 190 |

|    | 12.2  | Mem    | огу Мар                             | 191 |

|    | 12.3  | Repo   | ortable Errors                      | 191 |

|    | 12.4  | Func   | tional Description                  | 191 |

|    | 1     | 2.4.1  | BEU Global Interrupt                | 192 |

|    | 1     | 2.4.2  | BEU Local Interrupt                 | 192 |

|    | 1     | 2.4.3  | Global Interrupt Configuration      | 192 |

| 13 | Le    | vel 2  | Prefetcher                          | 193 |

|    | 13.1  | Oper   | ation                               | 193 |

|    | 13.2  | Retir  | ing Streams                         | 194 |

|    | 13.3  | Page   | Boundaries                          | 194 |

|    | 13.4  | Mem    | ory Map                             | 195 |

|    | 13.5  | Cont   | rol Registers                       | 195 |

| 14 | Le    | vel 2  | Cache Controller                    | 197 |

|    | 14.1  | Leve   | l 2 Cache Controller Overview       | 197 |

|    | 14.2 | Funct   | ional Description                                        | 197 |

|----|------|---------|----------------------------------------------------------|-----|

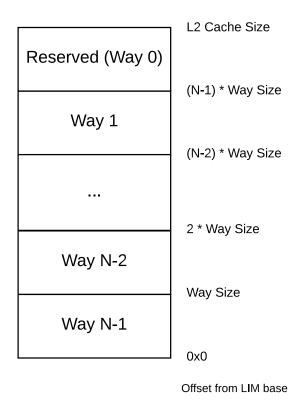

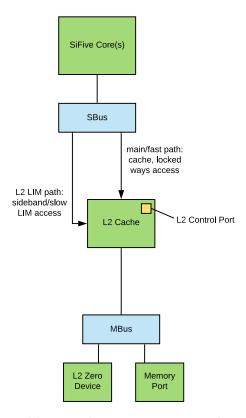

|    |      | 14.2.1  | Way Enable and the L2 Loosely-Integrated Memory (L2 LIM) | 198 |

|    |      | 14.2.2  | Way Masking and Locking                                  | 199 |

|    |      | 14.2.3  | L2 Zero Device                                           | 199 |

|    |      | 14.2.4  | L2 Features Access Summary                               | 201 |

|    |      | 14.2.5  | L2 Performance Monitor                                   | 201 |

|    |      | 14.2.6  | Error Correction Codes (ECC)                             | 206 |

|    |      | 14.2.7  | Coherence                                                | 207 |

|    | 14.3 | Memo    | ory Мар                                                  | 207 |

|    | 14.4 | Regis   | ter Descriptions                                         | 209 |

|    |      | 14.4.1  | L2 Cache Configuration Register (Config)                 | 209 |

|    |      | 14.4.2  | Way Enable Register (WayEnable)                          | 210 |

|    |      | 14.4.3  | ECC Error Injection Register (ECCInjectError)            | 210 |

|    |      | 14.4.4  | ECC Directory Fix Registers (DirECCFix*)                 | 210 |

|    |      | 14.4.5  | ECC Directory Fail Registers (DirECCFail*)               | 211 |

|    |      | 14.4.6  | ECC Data Fix Registers (DatECCFix*)                      | 211 |

|    |      | 14.4.7  | ECC Data Fail Registers (DatECCFail*)                    | 211 |

|    |      | 14.4.8  | L2 Cache ECC Error Injection and Correction              | 211 |

|    |      | 14.4.9  | Cache Flush Registers (Flush*)                           | 212 |

|    |      | 14.4.10 | Way Mask Registers (WayMask*)                            | 212 |

|    | 14.5 | Proce   | dure to Flush the L2 Cache                               | 214 |

|    | _    | _       |                                                          |     |

| 15 | Р    | ower I  | Management                                               |     |

|    | 15.1 | Powe    | r Modes                                                  | 216 |

|    | 15.2 | Run N   | Mode                                                     |     |

|    |      | 15.2.1  | Power Control                                            |     |

|    | 15.3 | WFI (   | Clock Gate Mode                                          |     |

|    |      | 15.3.1  | WFI Wake Up                                              |     |

|    | 15.4 | CEAS    | SE Instruction for Power Down                            | 218 |

|    | 15.5 |         | vare Reset                                               |     |

|    | 15.6 | Early   | Boot Flow                                                | 218 |

|    | 15.7 | Interr  | upt State During Early Boot                              | 219 |

|    | 15.8 | Other   | Boot Time Considerations                                 | 220 |

|    | 15.9 | Powe    | r-Down Flow                                        | . 220 |

|----|------|---------|----------------------------------------------------|-------|

| 16 | D    | ebug .  |                                                    | . 223 |

|    | 16.1 | •       | g Module                                           |       |

|    | 16.2 |         | g and Trigger Registers                            |       |

|    |      | 16.2.1  | Debug Control and Status Register (dcsr)           |       |

|    |      | 16.2.2  | Debug PC (dpc)                                     |       |

|    |      | 16.2.3  | Debug Scratch (dscratch)                           | .227  |

|    |      | 16.2.4  | Trigger Select Register (tselect)                  | .228  |

|    | ,    | 16.2.5  | Trigger Data Registers (tdata1-3)                  |       |

|    | 16.3 | Break   | points                                             | . 229 |

|    | :    | 16.3.1  | Breakpoint Match Control Register (mcontrol)       | .229  |

|    | :    | 16.3.2  | Breakpoint Match Address Register (maddress)       | .232  |

|    | :    | 16.3.3  | Breakpoint Execution                               | . 232 |

|    |      | 16.3.4  | Sharing Breakpoints Between Debug and Machine Mode | .232  |

|    | 16.4 | Debu    | g Memory Map                                       | . 232 |

|    | :    | 16.4.1  | Debug RAM and Program Buffer (0x300–0x3FF)         | .232  |

|    | :    | 16.4.2  | Debug ROM (0×800–0×FFF)                            | . 233 |

|    | :    | 16.4.3  | Debug Flags (0x100-0x110, 0x400-0x7FF)             | .233  |

|    | :    | 16.4.4  | Safe Address                                       | . 233 |

|    | 16.5 | Debu    | g Module Interface                                 | . 233 |

|    | :    | 16.5.1  | Debug Module Status Register (dmstatus)            | .234  |

|    | :    | 16.5.2  | Debug Module Control Register (dmcontrol)          | .235  |

|    | :    | 16.5.3  | Hart Info Register (hartinfo)                      | . 236 |

|    | :    | 16.5.4  | Hart Array Window Register (hawindow)              | .237  |

|    |      | 16.5.5  | Abstract Control and Status Register (abstractcs)  | .238  |

|    |      | 16.5.6  | Abstract Command Register (command)                | .239  |

|    |      | 16.5.7  | Abstract Command Autoexec Register (abstractauto)  | .239  |

|    | :    | 16.5.8  | Debug Module Control and Status 2 Register (dmcs2) | .239  |

|    | •    | 16.5.9  | Abstract Commands                                  | . 240 |

|    | :    | 16.5.10 | Multi-core Synchronization                         | .242  |

|    |      | 16.5.11 | System Bus Access                                  | . 242 |

|    | 16.6 | Debu    | g Module Operational Sequences                     | .242  |

|    | 1    | L6.6.1 | Entering Debug Mode                     | 242 |

|----|------|--------|-----------------------------------------|-----|

|    | 1    | L6.6.2 | Exiting Debug Mode                      | 243 |

| 17 | Er   | ror C  | Correction Codes (ECC)                  | 244 |

|    | 17.1 | ECC    | Configuration                           | 244 |

|    | 1    | L7.1.1 | ECC Initialization                      | 245 |

|    | 17.2 | ECC    | Interrupt Handling and Error Injection  | 245 |

|    | 17.3 | Hard   | dware Operation Upon ECC Error          | 245 |

| Α  | SiF  | ive (  | Core Complex Configuration Options      | 247 |

|    | A.1  | S7 S6  | eries                                   | 247 |

|    | A.2  | U7 S   | eries                                   | 250 |

| В  | SiF  | ive F  | RISC-V Implementation Registers         | 254 |

|    | B.1  | Mach   | ine Architecture ID Register (marchid)  | 254 |

|    | B.2  | Mach   | ine Implementation ID Register (mimpid) | 255 |

| С  | Flo  | atinç  | g-Point Unit Instruction Timing         | 256 |

|    | C.1  | S7 FI  | oating-Point Instruction Timing         | 256 |

|    | C.2  | U7 FI  | oating-Point Instruction Timing         | 258 |

| D  | Re   | visio  | n History                               | 261 |

| Re | fere | nces   |                                         | 262 |

# **Tables**

| Table 1                              | U74-MC Core Complex Feature Set                                                                                                                                                | 22 |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2                              | RISC-V Specification Compliance                                                                                                                                                | 26 |

| Table 3                              | Abbreviations and Terms                                                                                                                                                        | 28 |

| Table 4                              | S7 Feature Set                                                                                                                                                                 | 29 |

| Table 5                              | Executable Memory Regions for the U74-MC Core Complex                                                                                                                          | 30 |

| Table 6                              | S7 Instruction Latency                                                                                                                                                         | 34 |

| Table 7                              | pmpXcfg Bitfield Description                                                                                                                                                   | 38 |

| Table 8                              | pmpaddrX Encoding Examples for A=NAPOT                                                                                                                                         | 39 |

| Table 9                              | mhpmevent Register                                                                                                                                                             | 44 |

| Table 10                             | U7 Feature Set                                                                                                                                                                 | 47 |

| Table 11                             | Executable Memory Regions for the U74-MC Core Complex                                                                                                                          | 48 |

| Table 12                             | U7 Instruction Latency                                                                                                                                                         | 52 |

| Table 13                             | PTE Configuration Bits                                                                                                                                                         | 57 |

| Table 14                             | PTE Encoding fields                                                                                                                                                            | 58 |

| Table 15                             | satp.MODE Values                                                                                                                                                               | 59 |

| Table 16                             | pmpXcfg Bitfield Description                                                                                                                                                   | 68 |

| Table 17                             | pmpaddrX Encoding Examples for A=NAPOT                                                                                                                                         | 69 |

| Table 18                             | mhpmevent Register                                                                                                                                                             | 74 |

| Table 19                             | Physical Memory Attributes for External Regions                                                                                                                                | 79 |

| Table 20                             | Physical Memory Attributes for Internal Regions                                                                                                                                | 79 |

| <b>Table 21</b><br><b>X</b> –Execute | U74-MC Core Complex Memory Map. Physical Memory Attributes: <b>R</b> –Read, <b>W</b> –Write<br>e, <b>I</b> –Instruction Cacheable, <b>D</b> –Data Cacheable, <b>A</b> –Atomics |    |

| Table 22                             | Base Instruction Formats                                                                                                                                                       | 81 |

| Table 23                             | R-Type Integer Instructions                                                                                                                                                    | 83 |

| Table 24                             | R-Type Integer Instruction Description                                                                                                                                         | 83 |

| Table 25                             | I-Type Integer Instructions                                                                                                                                                    | 84 |

| Table 26                             | I-Type Integer Instruction Description                                                                                                                                         | 85 |

| Table 27                             | I-Type Load Instructions                                                                                                                                                       | 86 |

| Table 28                             | I-Type Load Instruction Description                                                                                                                                            | 86 |

| Table 29 | S-Type Store Instructions                                         | 87  |

|----------|-------------------------------------------------------------------|-----|

| Table 30 | S-Type Store Instruction Description                              | 87  |

| Table 31 | J-Type Instruction Description                                    | 88  |

| Table 32 | B-Type Instructions                                               | 88  |

| Table 33 | B-Type Instruction Description                                    | 88  |

| Table 34 | RISC-V Base Instruction to Assembly Pseudoinstruction Example     | 89  |

| Table 35 | Multiplication Operation Description                              | 90  |

| Table 36 | Division Operation Description                                    | 91  |

| Table 37 | Atomic Load-Reserve and Store-Conditional Instruction Description | 92  |

| Table 38 | Atomic Memory Operation Description                               | 93  |

| Table 39 | Accrued Exception Flags                                           | 93  |

| Table 40 | Floating-Point Rounding Modes                                     | 92  |

| Table 41 | Single-Precision FP Load and Store Instructions Description       | 92  |

| Table 42 | Single-Precision FP Computational Instructions Description        | 95  |

| Table 43 | Single-Precision FP Conversion Instructions Description           | 96  |

| Table 44 | Single-Precision FP to FP Sign-Injection Instructions Description | 97  |

| Table 45 | RISC-V Base Instruction to Assembly Pseudoinstruction Example     | 97  |

| Table 46 | Single-Precision FP Move Instructions Description                 | 97  |

| Table 47 | Single-Precision FP Compare Instructions Description              | 98  |

| Table 48 | Single-Precision FP Classify Instruction Description              | 98  |

| Table 49 | Floating-Point Number Classes                                     | 99  |

| Table 50 | Double-Precision FP Load and Store Instructions Description       | 99  |

| Table 51 | Double-Precision FP Computational Instructions Description        | 100 |

| Table 52 | Double-Precision FP Conversion Instructions Description           | 102 |

| Table 53 | Double-Precision FP to FP Sign-Injection Instructions Description | 103 |

| Table 54 | RISC-V Base Instruction to Assembly Pseudoinstruction Example     | 103 |

| Table 55 | Double-Precision FP Move Instructions Description                 | 104 |

| Table 56 | Double-Precision FP Compare Instructions Description              | 104 |

| Table 57 | Double-Precision FP Classify Instruction Description              | 105 |

| Table 58 | Stack-Pointed-Based Load Instruction Description                  | 106 |

| Table 59 | Stack-Pointed-Based Store Instruction Description                 | 107 |

| Table 60 | Register-Based Load Instruction Description                       | 107 |

| Table 61 | Register-Based Store Instruction Description                      | 108 |

| Table 62 | Unconditional Jump Instruction Description                 | 108 |

|----------|------------------------------------------------------------|-----|

| Table 63 | Unconditional Control Transfer Instruction Description     | 108 |

| Table 64 | Conditional Control Transfer Instruction Description       | 109 |

| Table 65 | Integer Constant-Generation Instruction Description        | 109 |

| Table 66 | Integer Register-Immediate Operation Description           | 110 |

| Table 67 | Integer Register-Immediate Operation Description (cont.)   | 110 |

| Table 68 | Integer Register-Immediate Operation Description (cont.)   | 110 |

| Table 69 | Integer Register-Immediate Operation Description (cont.)   | 110 |

| Table 70 | Integer Register-Immediate Operation Description (cont.)   | 111 |

| Table 71 | Integer Register-Register Operation Description            | 111 |

| Table 72 | Integer Register-Register Operation Description (cont.)    | 111 |

| Table 73 | Address Calculation Instructions Description               | 112 |

| Table 74 | Add/Shift with Prefix Zero-Extend Instructions Description | 113 |

| Table 75 | Count Leading/Trailing Zeroes Instructions Description     | 114 |

| Table 76 | Count Population Instructions Description                  | 114 |

| Table 77 | Logic-With-Negate Instructions Description                 | 115 |

| Table 78 | Comparison Instructions Description                        | 115 |

| Table 79 | Sign- and Zero-Extend Instructions                         | 116 |

| Table 80 | Bitwise Rotation Instructions Description                  | 117 |

| Table 81 | OR Combine Instruction Description                         | 117 |

| Table 82 | Byte-Reverse Instruction Description                       | 117 |

| Table 83 | Control and Status Register Instruction Description        | 118 |

| Table 84 | CSR Reads and Writes                                       | 119 |

| Table 85 | User Mode CSRs                                             | 120 |

| Table 86 | Supervisor Mode CSRs                                       | 121 |

| Table 87 | Machine Mode CSRs                                          | 122 |

| Table 88 | Debug Mode Registers                                       | 123 |

| Table 89 | Core Generator Encoding of marchid                         | 124 |

| Table 90 | Generator Release Encoding of mimpid                       | 125 |

| Table 91 | Timer and Counter Pseudoinstruction Description            | 126 |

| Table 92 | Timer and Counter CSRs                                     | 127 |

| Table 93 | RISC-V Registers                                           | 130 |

| Table 94 | RISC-V Assembly and C Examples                             | 131 |

| Table 95  | RISC-V Code Model Table                                       | 144 |

|-----------|---------------------------------------------------------------|-----|

| Table 96  | Branch Prediction Mode CSR                                    | 150 |

| Table 97  | SiFive Feature Disable CSR                                    | 151 |

| Table 98  | SiFive Feature Disable CSR Usage                              | 151 |

| Table 99  | Exception Priority                                            | 153 |

| Table 100 | Summary of Exception and Interrupt CSRs                       | 154 |

| Table 101 | Machine Status Register (partial)                             | 158 |

| Table 102 | Machine Trap Vector Register                                  | 159 |

| Table 103 | Encoding of mtvec.MODE                                        | 159 |

| Table 104 | Machine Interrupt Enable Register                             | 160 |

| Table 105 | Machine Interrupt Pending Register                            | 161 |

| Table 106 | Machine Cause Register                                        | 161 |

| Table 107 | mcause Exception Codes                                        | 162 |

| Table 108 | Machine Interrupt Delegation Register                         | 164 |

| Table 109 | Machine Exception Delegation Register                         | 164 |

| Table 110 | Supervisor Status Register (partial)                          | 165 |

| Table 111 | Supervisor Interrupt Enable Register                          | 165 |

| Table 112 | Supervisor Interrupt Pending Register                         | 166 |

| Table 113 | Supervisor Cause Register                                     | 166 |

| Table 114 | scause Exception Codes                                        | 167 |

| Table 115 | Supervisor Trap Vector Register                               | 168 |

| Table 116 | Encoding of stvec.MODE                                        | 168 |

| Table 117 | RNMI CSRs                                                     | 170 |

| Table 119 | U74-MC Core Complex Interrupt IDs                             | 175 |

| Table 120 | CLINT Memory Map                                              | 176 |

| Table 121 | PLIC Memory Map                                               | 180 |

| Table 122 | PLIC Interrupt Source Mapping                                 | 183 |

| Table 123 | Mapping of global_interrupts Signal Bits to PLIC Interrupt ID | 184 |

| Table 124 | PLIC Interrupt Priority Register                              | 184 |

| Table 125 | PLIC Interrupt Pending Register 1                             | 185 |

| Table 126 | PLIC Interrupt Pending Register 5                             | 185 |

| Table 127 | PLIC Interrupt Enable Register 1 for Hart 0 M-Mode            | 186 |

| Table 128 | PLIC Interrupt Enable Register 5 for Hart 0 M-Mode            | 186 |

| Table 129 | PLIC Clock Gate Disable Register                             | 186 |

|-----------|--------------------------------------------------------------|-----|

| Table 130 | PLIC Interrupt Priority Threshold Register                   | 187 |

| Table 131 | PLIC Claim/Complete Register for Hart 0 M-Mode               | 188 |

| Table 132 | Bus-Error Unit Memory Map                                    | 191 |

| Table 133 | Bus-Error Unit Error Events                                  | 191 |

| Table 134 | L2 Prefetcher Instances                                      | 193 |

| Table 135 | L2 Prefetcher Memory Map                                     | 195 |

| Table 136 | Basic Control Register                                       | 195 |

| Table 137 | Additional Control Register                                  | 196 |

| Table 138 | L2 Features Access Summary                                   | 201 |

| Table 139 | L2 Performance Monitor Event Selectors                       | 202 |

| Table 140 | L2 Performance Monitor Counter Client Filter                 | 202 |

| Table 141 | L2 Performance Monitor Counters                              | 203 |

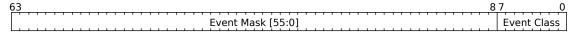

| Table 142 | L2PM pmEventSelect Register                                  | 204 |

| Table 143 | L2 Cache Controller Memory Map                               | 208 |

| Table 144 | L2 Cache Configuration Register                              | 209 |

| Table 145 | Way Enable Register                                          | 210 |

| Table 146 | ECC Error Injection Register                                 | 210 |

| Table 147 | Way Mask 0 Register                                          | 213 |

| Table 148 | Master IDs in the L2 Cache Controller                        | 214 |

| Table 149 | Power Dial Register                                          | 217 |

| Table 150 | Debug Module Memory Map Seen from the Debug Module Interface | 224 |

| Table 151 | Debug Module Memory Map from the Perspective of the Core     | 225 |

| Table 152 | Debug and Trigger Registers                                  | 226 |

| Table 153 | Debug Control and Status Register                            | 227 |

| Table 154 | Trigger Select Register                                      | 228 |

| Table 155 | Trigger Data Register 1                                      | 228 |

| Table 156 | Trigger Data Registers 2 and 3                               | 229 |

| Table 157 | Trigger CSRs When Used as Breakpoints                        | 229 |

| Table 158 | Breakpoint Match Control Register                            | 230 |

| Table 159 | NAPOT Size Encoding                                          | 231 |

| Table 160 | Debug Module Interface Signals                               | 234 |

| Table 161 | Debug Module Status Register                                 | 235 |

| Table 162 | Debug Module Control Register                                | .236  |

|-----------|--------------------------------------------------------------|-------|

| Table 163 | Hart Info Register                                           | . 237 |

| Table 164 | Abstract Control and Status Register                         | . 238 |

| Table 165 | Abstract Command Register                                    | . 239 |

| Table 166 | Abstract Command Autoexec Register                           | .239  |

| Table 167 | Debug Module Control and Status 2 Register                   | .240  |

| Table 168 | Debug Abstract Commands                                      | . 240 |

| Table 169 | Abstract Command Example for 32-bit Block Write              | .241  |

| Table 170 | System Bus vs. Program Buffer Comparison                     | .242  |

| Table 171 | Memory Protection Summary                                    | . 244 |

| Table 172 | Core Generator Encoding of marchid                           | . 254 |

| Table 173 | Generator Release Encoding of mimpid                         | . 255 |

| Table 174 | S7 Single-Precision FPU Instruction Latency and Repeat Rates | .257  |

| Table 175 | U7 Single-Precision FPU Instruction Latency and Repeat Rates | .258  |

| Table 176 | U7 Double-Precision FPU Instruction Latency and Repeat Rates | .259  |

| Table 177 | U74-MC Core Complex Manual Revision History                  | .261  |

# **Figures**

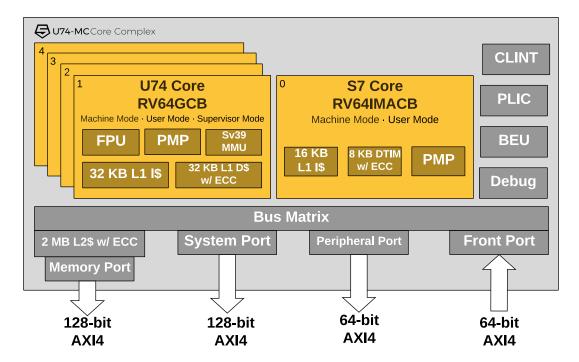

| Figure 1  | U7-MC Series Block Diagram                          | 24 |

|-----------|-----------------------------------------------------|----|

| Figure 2  | Example S7 Block Diagram                            | 33 |

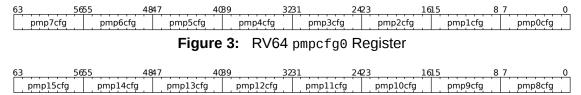

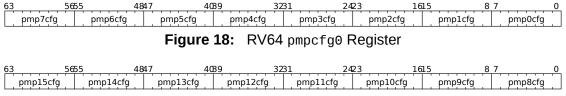

| Figure 3  | RV64 pmpcfg0 Register                               | 37 |

| Figure 4  | RV64 pmpcfg2 Register                               | 37 |

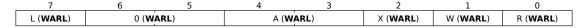

| Figure 5  | RV64 pmpXcfg bitfield                               | 37 |

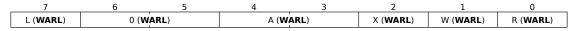

| Figure 6  | RV64 pmpaddrX Register                              | 39 |

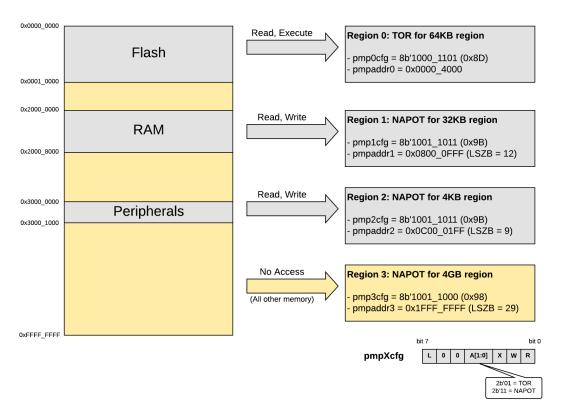

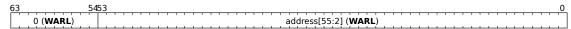

| Figure 7  | PMP Example Block Diagram                           | 40 |

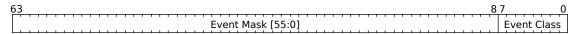

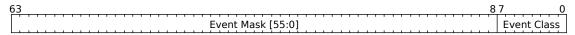

| Figure 8  | Event Selector Fields                               | 43 |

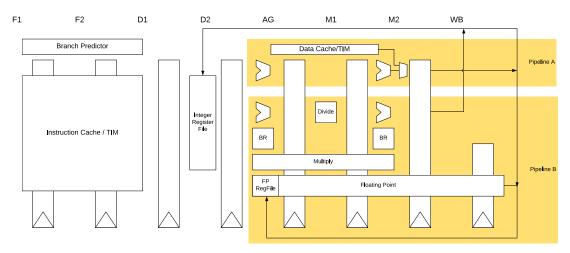

| Figure 9  | Example U7 Block Diagram                            | 51 |

| Figure 10 | TLB Update Flow                                     | 55 |

| Figure 11 | Sv39 Virtual Address                                | 56 |

| Figure 12 | Sv39 Physical Address                               | 56 |

| Figure 13 | Sv39 PTE Format                                     | 56 |

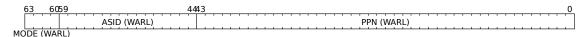

| Figure 14 | RV64 Supervisor Address Translation Register (satp) | 59 |

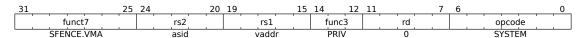

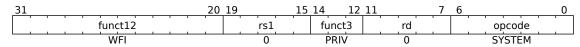

| Figure 15 | SFENCE.VMA Instruction                              | 60 |

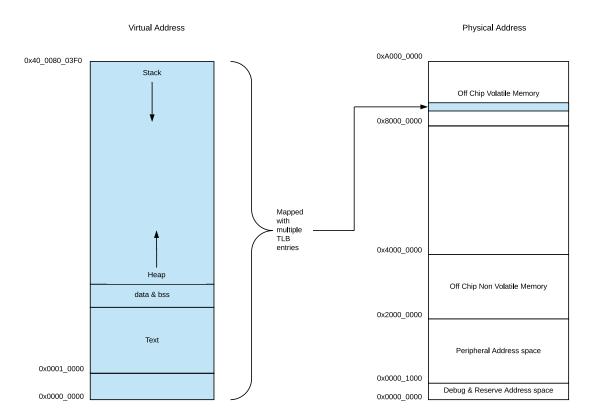

| Figure 16 | Linux User Application Memory Map Example           | 64 |

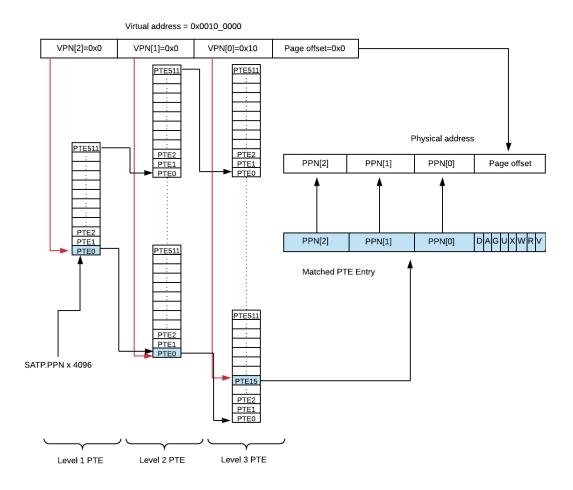

| Figure 17 | Hardware Table Walk Example                         | 65 |

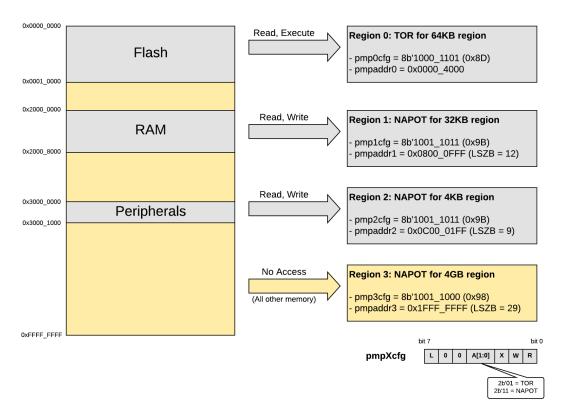

| Figure 18 | RV64 pmpcfg0 Register                               | 67 |

| Figure 19 | RV64 pmpcfg2 Register                               | 67 |

| Figure 20 | RV64 pmpxcfg bitfield                               | 67 |

| Figure 21 | RV64 pmpaddrX Register                              | 69 |

| Figure 22 | PMP Example Block Diagram                           | 70 |

| Figure 23 | Event Selector Fields                               | 73 |

| Figure 24 | R-Type                                              | 81 |

| Figure 25 | I-Type                                              | 82 |

| Figure 26 | S-Type                                              | 82 |

| Figure 27 | B-Type                                              | 82 |

| Figure 28 | U-Type                                              | 82 |

| Figure 29 | .1-Tvne                                             | 82 |

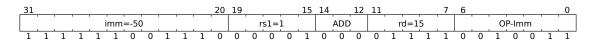

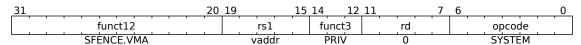

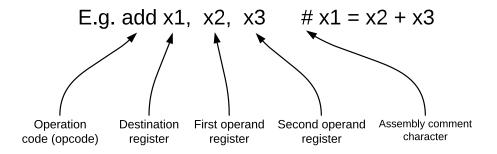

| Figure 30               | ADD Instruction Example                                                                       | 83         |

|-------------------------|-----------------------------------------------------------------------------------------------|------------|

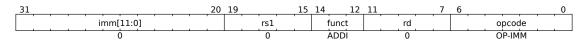

| Figure 31               | ADDI Instruction Example                                                                      | 85         |

| Figure 32               | LW Instruction Example                                                                        | 86         |

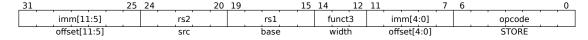

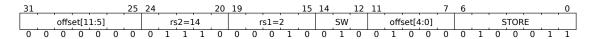

| Figure 33               | Store Instructions                                                                            | 86         |

| Figure 34               | SW Instruction Example                                                                        | 87         |

| Figure 35               | JAL Instruction                                                                               | 87         |

| Figure 36               | JALR Instruction                                                                              | 87         |

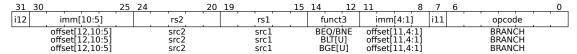

| Figure 37               | Branch Instructions                                                                           | 88         |

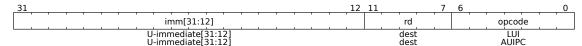

| Figure 38               | Upper-Immediate Instructions                                                                  | 89         |

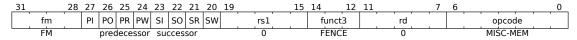

| Figure 39               | FENCE Instructions                                                                            | 89         |

| Figure 40               | NOP Instructions                                                                              | 90         |

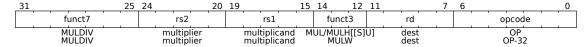

| Figure 41               | Multiplication Operations                                                                     | 90         |

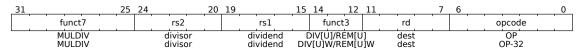

| Figure 42               | Division Operations                                                                           | 91         |

| Figure 43               | Atomic Operations                                                                             | 91         |

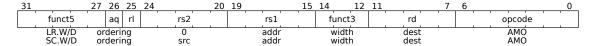

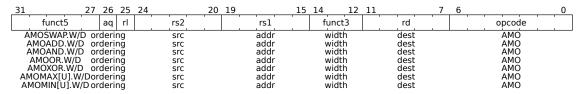

| Figure 44               | Atomic Memory Operations                                                                      | 92         |

| Figure 45               | Floating-Point Control and Status Register                                                    | 93         |

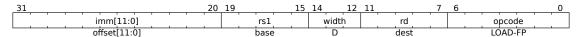

| Figure 46               | Single-Precision FP Load Instruction                                                          | 94         |

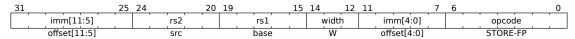

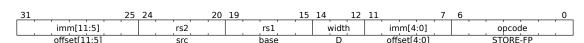

| Figure 47               | Single-Precision FP Store Instruction                                                         | 94         |

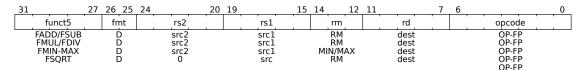

| Figure 48               | Single-Precision FP Computational Instructions                                                | 95         |

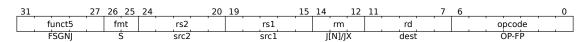

| Figure 49               | Single-Precision FP Fused Computational Instructions                                          | 95         |

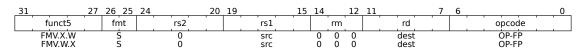

| Figure 50               | Single-Precision FP to Integer and Integer to FP Conversion Instructions                      | 95         |

| Figure 51               | Single-Precision FP to FP Sign-Injection Instructions                                         | 96         |

| Figure 52               | Single-Precision FP Move Instructions                                                         | 97         |

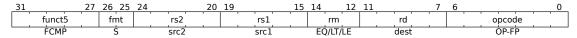

| Figure 53               | Single-Precision FP Compare Instructions                                                      | <b>9</b> 8 |

| Figure 54               | Single-Precision FP Classify Instruction                                                      | <b>9</b> 8 |

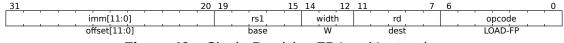

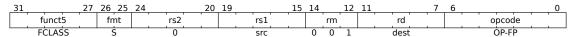

| Figure 55               | Double-Precision FP Load Instruction                                                          | 99         |

| Figure 56               | Double-Precision FP Store Instruction                                                         | 99         |

| Figure 57               | Double-Precision FP Computational Instructions                                                | . 100      |

| Figure 58               | Double-Precision FP Fused Computational Instructions                                          | .100       |

| Figure 59               | Double-Precision FP to Integer and Integer to FP Conversion Instructions                      | .101       |

| Figure 60<br>Conversion | Double-Precision to Single-Precision and Single-Precision to Double-Precision FP Instructions | . 101      |

| Figure 61               | Double-Precision FP to FP Sign-Injection Instructions                                         | .103       |

| Figure 62 | Double-Precision FP Move Instructions              | 103 |

|-----------|----------------------------------------------------|-----|

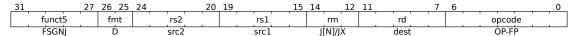

| Figure 63 | Double-Precision FP Compare Instructions           | 104 |

| Figure 64 | Double-Precision FP Classify Instruction           | 105 |

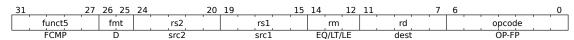

| Figure 65 | CR Format - Register                               | 105 |

| Figure 66 | CI Format - Immediate                              | 105 |

| Figure 67 | CSS Format - Stack-relative Store                  | 105 |

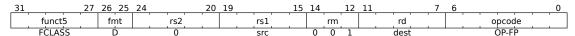

| Figure 68 | CIW Format - Wide Immediate                        | 105 |

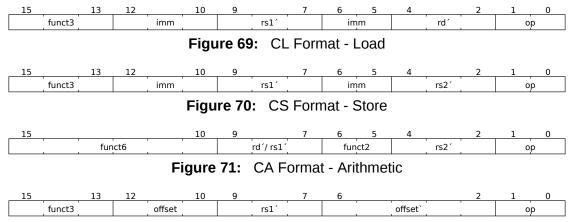

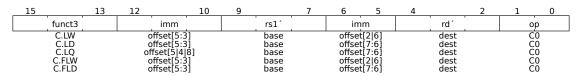

| Figure 69 | CL Format - Load                                   | 106 |

| Figure 70 | CS Format - Store                                  | 106 |

| Figure 71 | CA Format - Arithmetic                             | 106 |

| Figure 72 | CJ Format - Jump                                   | 106 |

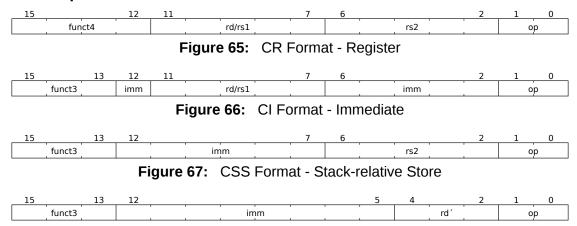

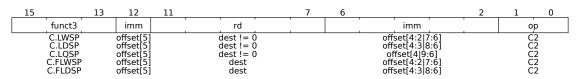

| Figure 73 | Stack-Pointed-Based Loads                          | 106 |

| Figure 74 | Stack-Pointed-Based Stores                         | 106 |

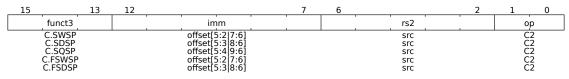

| Figure 75 | Register-Based Loads                               | 107 |

| Figure 76 | Register-Based Stores                              | 107 |

| Figure 77 | Unconditional Jump Instructions                    | 108 |

| Figure 78 | Unconditional Control Transfer Instructions        | 108 |

| Figure 79 | Conditional Control Transfer Instructions          | 109 |

| Figure 80 | Integer Constant-Generation Instructions           | 109 |

| Figure 81 | Integer Register-Immediate Operations              | 109 |

| Figure 82 | Integer Register-Immediate Operations (cont.)      | 110 |

| Figure 83 | Integer Register-Immediate Operations (cont.)      | 110 |

| Figure 84 | Integer Register-Immediate Operations (cont.)      | 110 |

| Figure 85 | Integer Register-Immediate Operations (cont.)      | 111 |

| Figure 86 | Integer Register-Register Operations               | 111 |

| Figure 87 | Integer Register-Register Operations (cont.)       | 111 |

| Figure 88 | Defined Illegal Instruction                        | 112 |

| Figure 89 | Address Calculation Instructions                   | 112 |

| Figure 90 | Address Calculation Instructions (cont.)           | 112 |

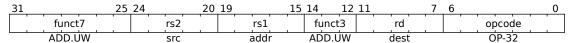

| Figure 91 | Add with Prefix Zero-Extend Instruction            | 113 |

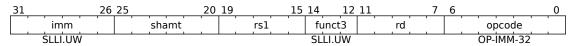

| Figure 92 | Shift with Prefix Zero-Extend Instruction          | 113 |

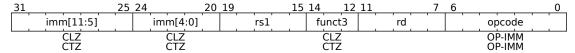

| Figure 93 | Count Leading/Trailing Zeroes Instructions         | 113 |

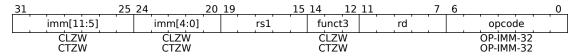

| Figure 94 | Count Leading/Trailing Zeroes Instructions (cont.) | 113 |

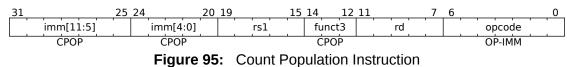

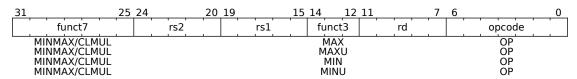

| Figure 95  | Count Population Instruction                             | 114 |

|------------|----------------------------------------------------------|-----|

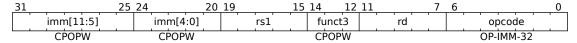

| Figure 96  | Count Population Instruction (cont.)                     | 114 |

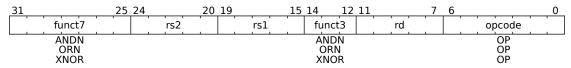

| Figure 97  | Logic-With-Negate Instructions                           | 114 |

| Figure 98  | Comparison Instructions                                  | 115 |

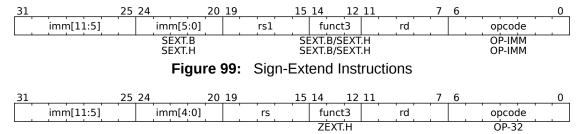

| Figure 99  | Sign-Extend Instructions                                 | 115 |

| Figure 100 | Zero-Extend Instruction                                  | 115 |

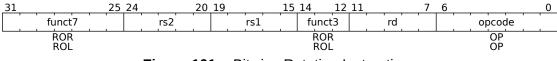

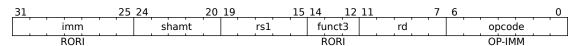

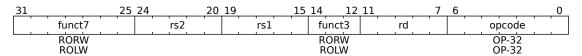

| Figure 101 | Bitwise Rotation Instructions                            | 116 |

| Figure 102 | Bitwise Rotation Instructions (cont.)                    | 116 |

| Figure 103 | Bitwise Rotation Instructions (cont.)                    | 116 |

| Figure 104 | Bitwise Rotation Instructions (cont.)                    | 116 |

| Figure 105 | Zicsr Instructions                                       | 118 |

| Figure 106 | Timer and Counter Pseudoinstructions                     | 126 |

| Figure 107 | ECALL and EBREAK Instructions                            | 128 |

| Figure 108 | Wait for Interrupt Instruction                           | 128 |

| Figure 109 | Supervisor Memory-Management Fence Instruction           | 129 |

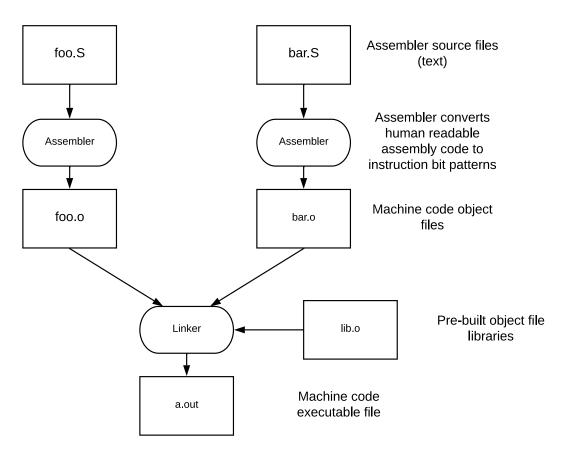

| Figure 110 | RISC-V Assembly Example                                  | 131 |

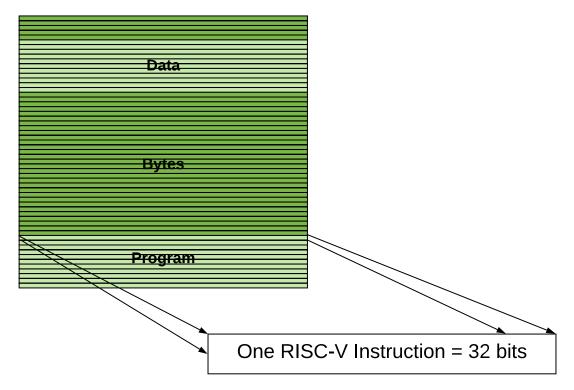

| Figure 111 | RISC-V Assembly to Machine Code                          | 132 |

| Figure 112 | One RISC-V Instruction                                   | 133 |

| Figure 113 | Stack Memory during Function Calls                       | 135 |

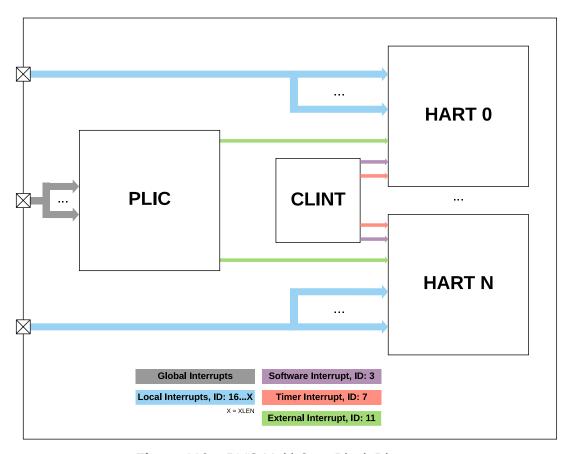

| Figure 114 | U74-MC Core Complex Interrupt Architecture Block Diagram | 156 |

| Figure 115 | CLINT Block Diagram                                      | 172 |

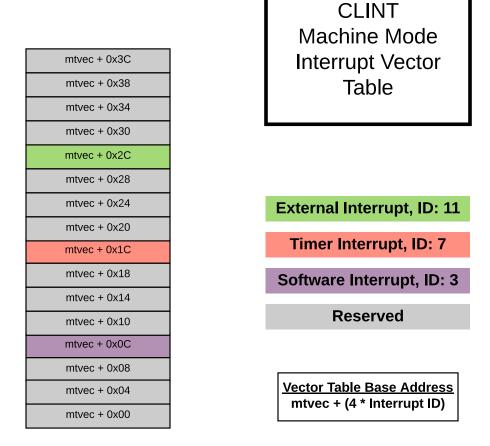

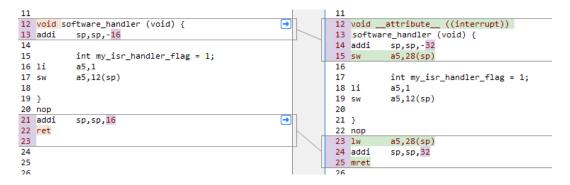

| Figure 116 | CLINT Interrupts and Vector Table                        | 173 |

| Figure 117 | CLINT Vector Table Example                               | 174 |

| Figure 118 | CLINT Interrupt Attribute Example                        | 175 |

| Figure 119 | PLIC Multi-Core Block Diagram                            | 179 |

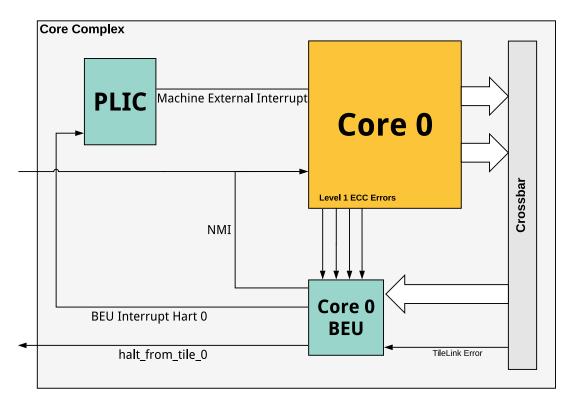

| Figure 120 | Bus-Error Unit Block Diagram                             | 190 |

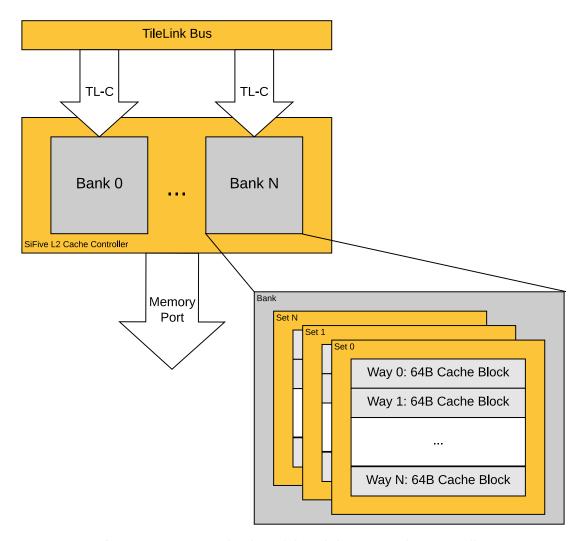

| Figure 121 | Organization of the SiFive L2 Cache Controller           | 198 |

| Figure 122 | Mapping of L2 Cache Ways to L2 LIM Addresses             | 199 |

| Figure 123 | Difference between L2 LIM and L2 Zero Device             | 200 |

| Figure 124 | Event Selector Fields                                    | 202 |

## Chapter 1

# Introduction

SiFive's U74-MC Core Complex is a full-Linux-capable, cache-coherent 64-bit RISC-V processor available as an IP block. The SiFive U74-MC Core Complex is guaranteed to be compatible with all applicable RISC-V standards, and this document should be read together with the official RISC-V user-level, privileged, and external debug architecture specifications.

A summary of features in the U74-MC Core Complex can be found in Table 1.

| U74-MC Core Complex Feature Set |                                                      |  |

|---------------------------------|------------------------------------------------------|--|

| Feature                         | Description                                          |  |

| Number of Harts                 | 5 Harts.                                             |  |

| S7 Core                         | 1 × S7 RISC-V core.                                  |  |

| U7 Core                         | 4 × U7 RISC-V cores.                                 |  |

| PLIC Interrupts                 | 127 Interrupt signals, which can be connected to     |  |

|                                 | off-core-complex devices.                            |  |

| PLIC Priority Levels            | The PLIC supports 7 priority levels.                 |  |

| Level 2 Cache                   | 2 MiB 16-way L2 Cache.                               |  |

| Hardware Breakpoints            | 2 hardware breakpoints.                              |  |

| Physical Memory Protection      | PMP with 8 regions and a minimum granularity of 4096 |  |

| Unit                            | bytes.                                               |  |

**Table 1:** U74-MC Core Complex Feature Set

The U74-MC Core Complex also has a number of on-core-complex configurability options, allowing one to tune the design to a specific application. The configurable options are described in Appendix A.

### 1.1 About this Document

This document describes the functionality of the U74-MC Core Complex 21G2.01.00. To learn more about the Evaluation RTL deliverables of the U74-MC Core Complex, consult the U74-MC Core Complex User Guide.

### 1.2 About this Release

This release of U74-MC Core Complex 21G2.01.00 is intended for evaluation purposes only. As such, the RTL source code has been intentionally obfuscated, and its use is governed by your Evaluation License.

The full list of technical limitations of the Evaluation U74-MC Core Complex can be found in the U74-MC Core Complex User Guide.

### 1.3 U74-MC Core Complex Overview

The U74-MC Core Complex includes  $1 \times S7$  and  $4 \times U7$  64-bit RISC-V cores, along with the necessary functional units required to support the cores. These units include a Core-Local Interruptor (CLINT) to support local interrupts, a Platform-Level Interrupt Controller (PLIC) to support platform interrupts, physical memory protection, a Debug unit to support a JTAG-based debugger host connection, and a local crossbar that integrates the various components together.

The U74-MC Core Complex memory system consists of a Data Cache, Data Tightly-Integrated Memory (DTIM), Instruction Cache, and Instruction Tightly-Integrated Memory (ITIM), with coherent L1 caches, shared L2 Cache, and a directory based coherence manager. The U74-MC Core Complex also includes a Front Port, which allows external masters to be coherent with the L1 memory system and access to the TIMs, thereby removing the need to maintain coherence in software for any external agents.

All memories, including caches and TIMs, support Single Error Correction, Double Error Detection (SECDED) ECC to provide improved reliability and address safety critical applications.

An overview of the SiFive U7-MC Series is shown in Figure 1. Refer to the docs/core\_complex\_configuration.txt file for a comprehensive summary of the U74-MC Core Complex configuration.

Figure 1: U7-MC Series Block Diagram

The U74-MC Core Complex memory map is detailed in Section 5.2, and the interfaces are described in full in the U74-MC Core Complex User Guide.

### 1.4 S7 RISC-V Monitor Core

The U74-MC Core Complex includes a 64-bit S7 RISC-V core, which has a dual-issue, in-order execution pipeline, with a peak execution rate of two instructions per clock cycle. The SiFive S7 core is guaranteed to be compatible with all applicable RISC-V standards.

The S7 core is configured to support the RV64I base ISA, as well as the Multiply (M), Atomic (A), Compressed (C), and Bit Manipulation (B) RISC-V extensions. This is captured by the RISC-V extension string: RV64IMACB. The base ISA and instruction extensions are described in Chapter 6.

The S7 also supports machine and user privilege modes, in conjunction with Physical Memory Protection (PMP), thereby allowing System-on-Chip (SoC) implementations to make the right area, power, and feature trade-offs.

The S7 core is designed to be feature rich, providing a very flexible memory system that includes L1 caches, Tightly-Integrated Memory (TIM), standards-based configurable bus interfaces, and memory maps that provide a lot of flexibility for SoC integration.

The microarchitecture also incorporates a branch prediction unit that is composed of a 16-entry Branch Target Buffer (BTB), a 3.6 KiB-entry Branch History Table (BHT), a 6-entry Return

Address Stack (RAS), 8-entry Indirect Jump Target Predictor (IJTP), and a 16-entry Return Instruction Predictor.

The S7 monitor core is described in more detail in Chapter 3.

### 1.5 U7 RISC-V Application Cores

The U74-MC Core Complex includes four 64-bit U7 RISC-V cores, which each have a dualissue, in-order execution pipeline, with a peak execution rate of two instructions per clock cycle. The SiFive U7 core is guaranteed to be compatible with all applicable RISC-V standards.

Each U7 core is configured to support the RV64I base ISA, as well as the Multiply (M), Single-Precision Floating Point (F), Double-Precision Floating Point (D), Atomic (A), Compressed (C), and Bit Manipulation (B) RISC-V extensions. This is captured by the RISC-V extension string: RV64GCB. The base ISA and instruction extensions are described in Chapter 6.

The U7 also supports machine, supervisor, and user privilege modes, in conjunction with Physical Memory Protection (PMP), thereby allowing System-on-Chip (SoC) implementations to make the right area, power, and feature trade-offs.

The U7 core is designed to be feature rich, providing a very flexible memory system that includes L1 caches, Tightly-Integrated Memory (TIM), standards-based configurable bus interfaces, and memory maps that provide a lot of flexibility for SoC integration.

The microarchitecture also incorporates a branch prediction unit that is composed of a 16-entry Branch Target Buffer (BTB), a 3.6 KiB-entry Branch History Table (BHT), a 6-entry Return Address Stack (RAS), 8-entry Indirect Jump Target Predictor (IJTP), and a 16-entry Return Instruction Predictor.

The U7 includes an IEEE 754-2008 compliant Floating-Point Unit.

The U7 application cores are described in more detail in Chapter 4.

### 1.6 Interrupts

The U74-MC Core Complex provides the standard RISC-V M-mode timer and software interrupts via the Core-Local Interruptor (CLINT).

The U74-MC Core Complex also includes a RISC-V standard Platform-Level Interrupt Controller (PLIC), which supports 136 global interrupts with 7 priority levels pre-integrated with the oncore-complex peripherals.

Interrupts are described in Chapter 8. The CLINT is described in Chapter 9. The PLIC is described in Chapter 10.

### 1.7 Debug Support

The U74-MC Core Complex provides external debugger support over an industry-standard JTAG port, including 2 hardware-programmable breakpoints per hart.

Debug support is described in detail in Chapter 16, and the debug interface is described in the U74-MC Core Complex User Guide.

### 1.8 Compliance

The U74-MC Core Complex is compliant to the following versions of the various RISC-V specifications:

| ISA                                                             | Version | Status   |

|-----------------------------------------------------------------|---------|----------|

| RV64I Base Integer Instruction Set                              | 2.0     | Frozen   |

| Extensions                                                      | Version | Status   |

| M Standard Extension for Integer Multiplication and Division    | 2.0     | Ratified |

| A Standard Extension for Atomic Instruction                     | 2.0     | Frozen   |

| F Standard Extension for Single-Precision Floating-Point        | 2.0     | Frozen   |

| D Standard Extension for Double-Precision Floating-Point        | 2.0     | Frozen   |

| C Standard Extension for Compressed Instruction                 | 2.0     | Ratified |

| Zba Standard Extension for Bit Manipulation                     | 0.94    |          |

| Zbb Standard Extension for Bit Manipulation                     | 0.94    |          |

| Privilege Mode                                                  | Version | Status   |

| Machine-Level ISA                                               | 1.11    |          |

| User-Level ISA                                                  | 1.11    |          |

| Supervisor-Level ISA                                            | 1.11    |          |

| Devices                                                         |         | Status   |

| The RISC-V Debug Specification                                  | 1.0     |          |

| RISC-V Platform-Level Interrupt Controller (PLIC) Specification | _       |          |

**Table 2:** RISC-V Specification Compliance

# **Chapter 2**

# **List of Abbreviations and Terms**

| Term     | Definition                                                                             |

|----------|----------------------------------------------------------------------------------------|

| BHT      | Branch History Table                                                                   |

| ВТВ      | Branch Target Buffer                                                                   |

| CLIC     | Core-Local Interrupt Controller. Configures priorities and levels for core-local       |

|          | interrupts.                                                                            |

| CLINT    | Core-Local Interruptor. Generates per hart software and timer interrupts.              |

| DTIM     | Data Tightly-Integrated Memory                                                         |

| Hart     | HARdware Thread                                                                        |

| IJTP     | Indirect-Jump Target Predictor                                                         |

| ITIM     | Instruction Tightly-Integrated Memory                                                  |

| JTAG     | Joint Test Action Group                                                                |

| LIM      | Loosely-Integrated Memory. Used to describe memory space delivered in a SiFive         |

|          | Core Complex that is not tightly integrated to a CPU core.                             |

| PLIC     | Platform-Level Interrupt Controller. The global interrupt controller in a RISC-V       |

|          | system.                                                                                |

| PMP      | Physical Memory Protection                                                             |

| RAS      | Return-Address Stack                                                                   |

| RO       | Used to describe a Read-Only register field                                            |

| RS       | Read/Set field. A register field that cannot be cleared by software, only reset will   |

|          | clear.                                                                                 |

| RW       | Used to describe a Read/Write register field                                           |

| RW1C     | Used to describe a Read/Write-1-to-Clear register field                                |

| TileLink | A free and open interconnect standard originally developed at UC Berkeley              |

| W1C      | Used to describe a Write-1-to-Clear register field                                     |

| WARL     | Write-Any, Read-Legal field. A register field that can be written with any value, but  |

|          | returns only supported values when read.                                               |

| WIRI     | Writes-Ignored, Reads-Ignore field. A read-only register field reserved for future     |

|          | use. Writes to the field are ignored and reads should ignore the value returned.       |

| WLRL     | Write-Legal, Read-Legal field. A register field that should only be written with legal |

| 11/0     | values and that only returns legal value if last written with a legal value.           |

| WO       | Used to describe a Write-Only register field                                           |

| WPRI     | Writes-Preserve, Reads-Ignore field. A register field that might contain unknown       |

|          | information. Reads should ignore the value returned, but writes to the whole           |

|          | register should preserve the original value.                                           |

Table 3: Abbreviations and Terms

# **Chapter 3**

# **S7 RISC-V Core**

This chapter describes the 64-bit S7 RISC-V processor core, instruction fetch and execution unit, L1 and L2 memory systems, Physical Memory Protection unit, Hardware Performance Monitor, and external interfaces.

The S7 feature set is summarized in Table 4.

| Feature                                      | Description                               |

|----------------------------------------------|-------------------------------------------|

| ISA                                          | RV64IMACB                                 |

| SiFive Custom Instruction Extension (SCIE)   | Not Present                               |

| Modes                                        | Machine mode, user mode                   |

| L1 Instruction Cache                         | 16 KiB 2-way instruction cache            |

| Instruction Tightly-Integrated Memory (ITIM) | 16 KiB ITIM                               |

| Data Tightly-Integrated Memory (DTIM)        | 8 KiB DTIM                                |

| L2 Cache                                     | 2 MiB 16-way L2 cache with 2 banks        |

| ECC Support                                  | Single error correction, double error     |

|                                              | detection on the ITIM, DTIM, and L2 cache |

| Fast I/O                                     | Present                                   |

| Physical Memory Protection                   | 8 regions with a granularity of 64 bytes  |

**Table 4:** S7 Feature Set

### 3.1 Supported Modes

The S7 supports RISC-V user mode, providing two levels of privilege: machine (M) and user (U). U-mode provides a mechanism to isolate application processes from each other and from trusted code running in M-mode.

See *The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Version 1.10* for more information on the privilege modes.

### 3.2 Instruction Memory System

This section describes the instruction memory system of the S7 Monitor core.

#### 3.2.1 Execution Memory Space